## Evaluating Neural Networks on Low Powered GPUs.

Simon Rovder

Master of Informatics

School of Informatics University of Edinburgh

2017

## Abstract

This report presents optimisation techniques for improving neural network execution performance on low-powered GPUs. Specifically targeting the Odroid-XU3 board, the report demonstrates the performance of variously optimised OpenCL kernels for forward propagating inputs over a fully-connected neural network using the Mali T-628 GPU present on the Odroid board.

We write a framework for testing general-purpose OpenCL kernels on GPUs, on top of which the neural network execution system is subsequently built.

Considered optimisation techniques include altering memory layouts, managing workgroup sizes, vectorisation, and cache blocking. We reproduce the results of the best performing matrix multiplication kernel published by ARM for this GPU, and improve its performance by 12% using Hybrid Morton Order memory layouts.

The final system is benchmarked against TensorFlow on a desktop GPU as well as Numpy on the CPU of the Odroid Board. In both cases the system demonstrates promissing results, matching TensorFlow in performance on small networks and greatly outperforming Numpy for any network.

## Acknowledgements

I would like to thank Michael O'Boyle for his support and guidance over the course of this project.

Further thanks goes to James Renwick for always gladly providing insight into the intricacies of C++.

I would also like to thank Constance Crowe and Paul Sinclair for proofreading my final report draft.

# **Table of Contents**

| 1 | Intr                                                        | oduction                                                                                                                                                                                                                | 7                                                         |  |  |

|---|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|

|   | 1.1                                                         | Goal                                                                                                                                                                                                                    | 7                                                         |  |  |

|   | 1.2                                                         | Motivation                                                                                                                                                                                                              | 8                                                         |  |  |

| 2 | Background                                                  |                                                                                                                                                                                                                         |                                                           |  |  |

|   | 2.1                                                         | Neural Networks                                                                                                                                                                                                         | 9                                                         |  |  |

|   | 2.2                                                         | Graphic Processing Units (GPUs)                                                                                                                                                                                         | 12                                                        |  |  |

|   | 2.3                                                         | OpenCL                                                                                                                                                                                                                  | 12                                                        |  |  |

|   | 2.4                                                         | The Mali-T628 GPU on the Odroid XU-3 board                                                                                                                                                                              | 15                                                        |  |  |

|   | 2.5                                                         | Mali GPUs compared to Desktop GPUs                                                                                                                                                                                      | 16                                                        |  |  |

| 3 | Rela                                                        | ited Work                                                                                                                                                                                                               | 19                                                        |  |  |

|   | 3.1                                                         | Machine Learning and GPUs                                                                                                                                                                                               | 19                                                        |  |  |

|   | 3.2                                                         | Neural Network Frameworks                                                                                                                                                                                               | 20                                                        |  |  |

|   | 3.3                                                         | Optimising GPU kernels                                                                                                                                                                                                  | 20                                                        |  |  |

|   | 3.4                                                         | Optimization Techniques for Mali GPUs                                                                                                                                                                                   | 20                                                        |  |  |

|   | 3.5                                                         | Mali T-600 Series Matrix Multiplication                                                                                                                                                                                 | 21                                                        |  |  |

|   | 3.6                                                         | CNNdroid                                                                                                                                                                                                                | 21                                                        |  |  |

| 4 | Infr                                                        | astructure                                                                                                                                                                                                              | 23                                                        |  |  |

|   | 4.1                                                         | Motivation                                                                                                                                                                                                              | 23                                                        |  |  |

|   | 4.2                                                         | The CLStruct                                                                                                                                                                                                            | 24                                                        |  |  |

|   |                                                             |                                                                                                                                                                                                                         |                                                           |  |  |

|   | 4.3                                                         | The CLManager                                                                                                                                                                                                           | 25                                                        |  |  |

|   | 4.3<br>4.4                                                  | The CLManager                                                                                                                                                                                                           | 25<br>25                                                  |  |  |

|   |                                                             |                                                                                                                                                                                                                         | -                                                         |  |  |

|   | 4.4                                                         | The DynamicCL::Kernel wrapper                                                                                                                                                                                           | 25<br>27                                                  |  |  |

| 5 | 4.4<br>4.5<br>4.6                                           | The DynamicCL::Kernel wrapper                                                                                                                                                                                           | 25<br>27<br>28                                            |  |  |

| 5 | 4.4<br>4.5<br>4.6                                           | The DynamicCL::Kernel wrapper         Mirrorable         Summary                                                                                                                                                        | 25                                                        |  |  |

| 5 | 4.4<br>4.5<br>4.6<br><b>Neu</b>                             | The DynamicCL::Kernel wrapper                                                                                                                                                                                           | 25<br>27<br>28<br><b>29</b>                               |  |  |

| 5 | 4.4<br>4.5<br>4.6<br><b>Neu</b><br>5.1                      | The DynamicCL::Kernel wrapper         Mirrorable         Summary         Summary         ral Network Execution System         The CLMatrix                                                                              | 25<br>27<br>28<br><b>29</b><br>30                         |  |  |

| 5 | 4.4<br>4.5<br>4.6<br><b>Neu</b><br>5.1<br>5.2               | The DynamicCL::Kernel wrapper         Mirrorable         Summary         Summary         ral Network Execution System         The CLMatrix         Performers and Operations                                            | 25<br>27<br>28<br><b>29</b><br>30<br>30                   |  |  |

| 5 | 4.4<br>4.5<br>4.6<br><b>Neu</b><br>5.1<br>5.2<br>5.3        | The DynamicCL::Kernel wrapper         Mirrorable         Summary         Summary         ral Network Execution System         The CLMatrix         Performers and Operations         The Neural Network         Summary | 25<br>27<br>28<br><b>29</b><br>30<br>30<br>32             |  |  |

|   | 4.4<br>4.5<br>4.6<br><b>Neu</b><br>5.1<br>5.2<br>5.3<br>5.4 | The DynamicCL::Kernel wrapper         Mirrorable         Summary         Summary         ral Network Execution System         The CLMatrix         Performers and Operations         The Neural Network         Summary | 25<br>27<br>28<br><b>29</b><br>30<br>30<br>30<br>32<br>34 |  |  |

|     | 6.3    | Bias Addition                                         |

|-----|--------|-------------------------------------------------------|

|     | 6.4    | Evaluation                                            |

|     | 6.5    | Summary 39                                            |

| 7   | Opti   | mizing the Matrix Multiplication 41                   |

|     | 7.1    | Memory Layouts                                        |

|     | 7.2    | Workgroup Sizes                                       |

|     | 7.3    | Vectorisation                                         |

|     | 7.4    | Blocking                                              |

|     | 7.5    | Summary 51                                            |

| 8   | Mor    | con Order Memory Layouts 53                           |

|     | 8.1    | Hybrid Morton Order Layouts                           |

|     | 8.2    | Computing Hybrid Morton Order Indices                 |

|     | 8.3    | Implementation                                        |

|     | 8.4    | Hybrid Morton Order Matrix Multiplication             |

|     | 8.5    | Evaluation                                            |

|     | 8.6    | Summary                                               |

| 9   | Opti   | misation of Bias Addition and Activation Functions 63 |

|     | 9.1    | Bias Addition                                         |

|     | 9.2    | Activation Functions                                  |

|     | 9.3    | Summary                                               |

| 10  | Eval   | uation 69                                             |

|     |        | TensorFlow                                            |

|     |        | Numpy                                                 |

|     |        | Summary                                               |

| 11  |        |                                                       |

| 11  |        | Susion 73                                             |

|     |        | Critical Analysis                                     |

|     | 11.2   | Future Work                                           |

| Bił | oliogr | aphy 75                                               |

| 12  | Арре   | endix 79                                              |

|     | 12.1   | CLManager Interface                                   |

|     | 12.2   | Blocked $RM \times RM$ Matrix Multiplication Kernel   |

|     | 12.3   | Blocked RM $\times$ CM Matrix Multiplication Kernel   |

|     | 12.4   | Order of workgroup computation                        |

|     |        | Complex Hybrid Morton Order Memory Layouts            |

|     |        | Morton 4-4 Kernel                                     |

|     |        | Morton 4-2 Kernel                                     |

|     | 12.8   | Memory Access Pattern Notation                        |

|     | 12.9   | Other Kernels                                         |

|     |        |                                                       |

# **Chapter 1**

## Introduction

Neural networks have repeatedly proved their use in the field of Machine Learning. Being adaptable to a large variety of problems, neural networks have yielded state of the art results in pattern recognition and classification tasks such as image recognition [1] and speech processing [2]. For certain problems, neural networks have even been trained to outperform professional human predictions [3].

Until recently, the computational complexity of training and executing neural networks posed a significant problem to their wide-spread use. However, with the progressing performance improvements of Graphics Processing Units (GPUs), technology has caught up with the computational demands of neural networks and we are beginning to be able to effectively harness their potential.

In recent years GPUs made their way into the hand-held devices market of spartphones and tablets <sup>1</sup>. These low powered GPUs open doors for making use of neural networks on these devices.

## 1.1 Goal

The goal of this work is to create a simple system for executing neural networks on low powered GPUs. The target device of this research is the Mali T-628 GPU on the Odroid XU-3 board. We shall write an OpenCL implementation of the basic essential operations needed to execute fully-connected neural networks and we tailor these kernels to exploit the architectural hardware optimisations present on this particular device.

The most computationally expensive task we tackle is matrix multiplication. Our goal is to reproduce the performance of the best performing Mali T-628 matrix multiplication kernel published by ARM and improve upon it. This goal is successfully accomplished in Chapter 8, where we use Hybrid Morton Order memory layouts to outperform the ARM implementation performance by 12%.

<sup>&</sup>lt;sup>1</sup>A concise list of smartphone and tablet GPUs has been compiled by Klaus Hinum[4]

## 1.2 Motivation

As mentioned previously, low powered GPUs have become popular in the field of hand-held devices. There is, however, a notable lack of research in the area of optimising neural network execution on these devices. Most research today focuses on the issue of efficient training of neural networks, which is a much more expensive endeavor, and as such regular desktop GPUs are the preferred tool for this task.

One of the forefront frameworks for executing neural networks of GPUs is TensorFlow. TensorFlow, however, works on the CUDA architecture, meaning it cannot execute on the Mali T-628 GPU. Given the popularity of TensorFlow, it is understandable that a similar demand exists for OpenCL platforms. The lack of OpenCL support is a long standing issue with TensorFlow [5], as well as other similar frameworks further discussed in Section 3.2.

This work hence aims to fill this gap in the field of GPU machine learning research.

# **Chapter 2**

## Background

### 2.1 Neural Networks

The concept of today's neural networks dates back to the 1950s and the invention of the perceptron. This section gives a brief introduction to the topic and describes the principles behind a simple fully-connected neural network.

### 2.1.1 The Perceptron

The fundamental building block of neural networks is the perceptron. The perceptron is a computational representation of a multidimensional binary classifier that mimics the functioning of a biological neuron. It takes a set of values as inputs (much like a neuron does via dendrites) and outputs a single value (much like a neuron does via the axon).

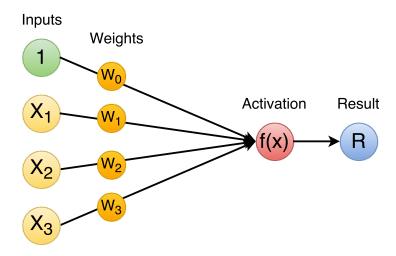

Suppose we had a perceptron that processes *N* dimensional input vectors with entries  $\alpha_1...\alpha_N$ . In addition to this, the perceptron will add an  $a_0 = 1$  entry to this vector (also known as the *bias* term). For each  $a_i$ , the perceptron will have a *weight* term  $w_i$ . The perceptron will then calculate its output *r* as seen in Equation 2.1. A visualisation of a perceptron can be seen in Figure 2.1.

$$r = f\left(\sum_{i=0}^{N} w_i a_i\right)$$

where

$$f(x) = \begin{cases} 1 & x \ge 0\\ 0 & otherwise \end{cases}$$

Equation 2.1: Perceptron Computation

Figure 2.1: Perceptron Diagram - Capable of classifying linearly separable data.

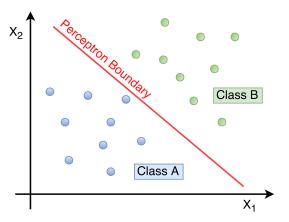

The resulting binary classification achieved by a perceptron splits the input space between the two classes. An example of such a split of a two dimensional input space can be seen in Figure 2.2. Note that this boundary is linear. A perceptron is only capable of splitting the input space into two regions linearly, where the boundary is decided by the weights.

#### 2.1.2 Fully-Connected Layers

The output of a single perceptron conveys a single piece of information about the input feature vector. Complex classification problems often require more information about the input vector, which is why perceptron are rarely used individually. The common approach to extracting more information from an input vector is to pass it to multiple perceptron, collecting the outputs into an output vector. Suppose we had an *n*-dimensional input vector *V* and an *m* dimensional vector *R*. The individual values  $R_i$  are computed as follows:

$$R_i = f\left(\sum_{k=0}^n \left(V_k w_{ik}\right)\right)$$

In this formula,  $w_{ij}$  is the weight connecting  $V_i$  to  $R_j$ , which means we are effectively linearly transforming V by computing  $W \times V$  for a matrix W where  $W_{ij} = w_{ji}$ . In addition, the function f may be replaced with any other activation function (popular choices including Sigmoid and ReLU functions), to introduce non-linearity.

#### 2.1. Neural Networks

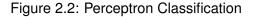

Figure 2.3: Diagram of a deep neural network - Capable of classifying non-linearly separable data.

### 2.1.3 Deep Neural Networks

The issue with the perceptron layer approach from Section 2.1.2 is that, despite the model having greater classification power than a single perceptron, it still cannot classify non-linearly separable classes. This is solved by chaining multiple perceptron layers sequentially into what we call **deep neural networks**, which enables the classifier to separate data which is not necessarily linearly separable. This process is called **feature extraction**, as the first layer of perceptrons extract **features** from the input vector, such that these higher-level features allow linear separability of classes, or convey less featurally entangled classes (closer to linearly separable).

Due to this ability to perform feature extraction and learn which features to extract, a deep neural network is superior to a single layer network, allowing it to be applied to more complex problems. A visual representation of a deep neural network can be seen in Figure 2.3.

Given propagating an input vector over a single layer requires matrix multiplication, and multiple layers connected sequentially, it is understandable that executing neural networks is a highly computationally demanding task. This is especially true for high dimensional data that may have dimensionality in the order of thousands (for example for images).

It is for this reason that GPUs are often utilized to tackle the most computationally intensive operations of this process.

### 2.2 Graphic Processing Units (GPUs)

Primarily motivated by the growth of the video game industry, GPUs have steadily improved and became integral parts of many audio-visual devices, which, in recent years, also includes hand-held devices like smartphones. Although GPUs were primarily designed with the purpose of graphics processing, their computational power can be employed for any data-based parallelisable task.

There are two primary types of parallelism: **task-based** parallelism and **data-based** parallelism. Task-based parallelism is the kind we are most familiar with from interacting with computers in every day life: having multiple different programs running at the concurrently, each working on achieving its own goal. Data-based parallelism is the type of parallelism used by GPUs to process data: having a single program run many times with each instance processing different data (or different sections of the same data), for the most part with the intention of eventually combining their partial results into one final result.

Data-based parallelism is highly effective at executing tasks which require a large amount of number crunching, which is why GPUs are a great candidate device for executing neural networks.

## 2.3 OpenCL

OpenCL [6] is a framework for writing and executing code in parallel across multiple heterogeneous platforms and we shall make use of it in this work to execute programs on the Mali GPU. The OpenCL programming paradigm focuses on splitting a program into **host-code** and **device-code**.

**Host-code** is the part of the program intended to run on the CPU, and usually comprises of the sequential infrstructural code. It can be written in any language, provided OpenCL bindings are available for this language. <sup>1</sup>

**Device-code** is the part of the program intended to run in parallel on the GPU. OpenCL defines its own programming language for device-code (which is closely based on C-99) and is compiled by OpenCL at runtime for individual devices. This OpenCL code can be stored in strings or in separate files.

<sup>&</sup>lt;sup>1</sup>Bindings have been written for many programming languages, most popular of which include Java [7], Python [8] and Haskell [9]. In our work we use C++ bindings [10].

### 2.3.1 Terminology

This section introduces all terminology related to OpenCL.

- **OpenCL Device** A hardware component capable of executing OpenCL code. An example is the Mali T-628 GPU itself. Other examples are regular graphics cards in computers (such as NVIDIA or RADEON cards), integrated graphics devices, coprocessors, even CPUs themselves are also usually compliant with OpenCL. An OpenCL Device will contain one or more *Compute Units*.

- **Compute Unit (or** *Core***)** A piece of hardware capable of executing a *Kernel* on a *Workgroup*. An OpenCL Device will usually have one or more of these.

- **Kernel** A single function from the device-code. Host-code will run the Kernel in parallel on the OpenCL device.

- Workgroup A set of Work Items, small enough to execute on a single compute unit.

- Work Item A particular instantiation of a kernel. When executing, every kernel has its own set of *ids* (this is what we mean by its *instantiation*). The kernel accesses these ids via function calls and once it knows their values, the kernel knows what it should do.

- **NDRange** The term for the range of ids a kernel is mapped onto. (Stands for N-Dimensional Range).

### 2.3.2 OpenCL Paradigm

In order to understand how and when OpenCL can be used, one must first understand the principle behind its functionality. What OpenCL achieves is best demonstrated on an example.

Suppose we wanted to add two 2-dimensional matrices together. In C++ we could write a program for this task as seen in Figure 2.4.

```

1 void addMatrices(Matrix& a, Matrix& b, Matrix& r){

2 for(size_t row = 0; row < a.rows; row++) {

3 for(size_t col = 0; col < a.cols; col++) {

4         r[row][col] = a[row][col] + b[row][col];

5     }

6     }

7 }</pre>

```

Figure 2.4: Example unparallelised C++ matrix addition algorithm

The code in Figure 2.4 will successfully execute the task, however, it will do so sequentially in a single thread on the CPU (computing one sum at a time). However, if we think about this code in terms of utility, we observe that the only line in this implementation directly contributing to the computation of our desired result is line 4. The for loops are there only as boilerplate; they ensure that line 4 gets called for all combinations of row and col.

Hypothetically, if one was able to execute line 4 from Figure 2.4 in parallel for *all* combinations of row and col at the same time, the same result would be achieved. In other words we want something resembling code in Figure 2.5.

```

1 parallel void addMatrices(Matrix& a, Matrix& b, Matrix& r){

2 size_t row = whichRow();

3 size_t col = whichCol();

4 r[row][col] = a[row][col] + b[row][col];

5 }

```

Figure 2.5: Pseudocode representation of a parallel matrix addition program

The code in Figure 2.5 is conceptually very close to what OpenCL does. OpenCL allows us to map a function onto a space of  $ids^2$ , which are then accessible from the code via function calls. For our example these ids would be the combinations of rows and columns. A full OpenCL implementation of this algorithm (for reference and contrasting) can be seen in Figure 2.6

```

1

___kernel void addMatrices(

2

size_t cols,

3

const float * a,

4

const float * b,

5

float * r )

6

{

7

size_t row = get_global_id(0);

8

size_t col = get_global_id(1);

9

r[row*cols + col] =

10

a[row*cols + col] + b[row*cols + col];

11

}

```

#### Figure 2.6: OpenCL implementation of a parallel matrix addition program

<sup>&</sup>lt;sup>2</sup>The space of ids can be one, two or three dimensional. In the case of matrix addition, we would choose a two-dimensional space.

|                     | Device 1      | Device 2      |

|---------------------|---------------|---------------|

| Memory (bytes)      |               |               |

| Global              | 2 091 724 800 | 2 091 724 800 |

| Cache size          | 131 072       | 131 072       |

| Cacheline size      | 64            | 64            |

| Cachelines          | 2048          | 2048          |

| Local               | 32768         | 32768         |

| Vector Sizes        |               |               |

| Char                | 16            | 16            |

| Short               | 8             | 8             |

| Int                 | 4             | 4             |

| Long                | 2             | 2             |

| Float               | 4             | 4             |

| Double              | 2             | 2             |

| Computation         |               |               |

| Clock               | 600 Mhz       | 600 Mhz       |

| Compute units       | 4             | 2             |

| Max work group size | 256           | 256           |

| Work item sizes     | 256, 256, 256 | 256, 256, 256 |

Table 2.1: Specifications of the two OpenCL devices available on the MALI T-628 GPU.

### 2.4 The Mali-T628 GPU on the Odroid XU-3 board

In this project we will be optimising neural network execution for one specific device - the **Odroid-XU3** board. This board contains one physical Mali T-628 GPU, although its compute units are accessible via two separate devices.

To properly optimise algorithms for the GPU, we need to know what hardware restrictions it imposes. Since the specifications may vary between the two accessible devices, in order to have reliable knowledge of the device specifications, we need to investigate both devices ourselves. The C++ bindings for OpenCL provides us with a simple interface for querying the devices for their hardware capabilities with the getInfo method. We have queried both the device for their specifications. These can be seen in Table 2.1.

As you can see in Table 2.1, the only difference between the two devices is the amount of compute units. The first device has twice as many compute units as the second one. This means that the first device can process four workgroups at a time, while the second one can only process two and we may need to take this into consideration when optimising for each individually.

The final relevant metric to the Mali T-628 GPU is the **GFLOPS** (amount of billions of floating point operations performed per second) limit, which is 17 GFLOPS per Compute Unit [11].

## 2.5 Mali GPUs compared to Desktop GPUs

Every GPU has its own internal architecture, yet they usually adhere to certain common standards, which software engineers expect and rely on when writing device code. The Mali GPU is a low-powered GPU and it architecturally differs from common desktop GPUs, meaning that many techniques used to optimise device code for common GPUs may not work (or may even have an explicitly negative impact) when used in Mali device code. Similarly, certain uncommon optimisation techniques may have a much more pronounced positive impact on the Mali than on a desktop GPU. In this section we present the key differences between the Mali and other more common desktop GPUs.

### 2.5.1 Local Memory

The main task of GPUs is to do a large amount of data processing and number crunching concurrently. On a GPU, prior to processing, this data will be placed into the device's **global memory**, from which the cores of the GPU can access it. This global memory may be understood as something resembling Random Access Memory (RAM) in the context of a CPU. As mentioned in Secton 2.3.1, a device may have multiple cores, each capable of executing many concurrent work items, and often parts of data used by one work item may also be required by another work item.

**Desktop GPUs** exploit this data reusability using *local memory*. Local memory is a hardware component for storing data and it is located directly on the chip, one within each core. Thus one may set up workgroups such that the individual work items' data requirement overlaps are maximised. This allows us to write kernels which, before performing any processing, collectively copy the required data from global memory to local memory, making only a single access to global memory per datum. Then, the kernels may proceed to process the data, accessing it in the faster local memory, mitigating the requests to global memory (and allowing other cores to access it).

The Mali GPUs do not have any on-chip local memory. One may still use local memory, however, it is mapped to the same hardware as global memory. This means local memory is not suitable for optimisations purely for improving data access speed and any such optimisations will only have a negative overhead effect. On the other hand, Mali GPUs make heavy use of caching and optimising for cache size and cache line size is desired [12].

### 2.5.2 Thread Divergence

In GPUs, massive parallelism is achieved by having small groups of threads run on the same program counter. This, of course, introduces problems when execution reaches an inconsistent branch instruction, where GPUs will cause threads to stall (as program counter is no longer identical). This is called *thread divergence*.

**Desktop GPUs** rely on the programmer to write code to avoid thread divergence. In turn, architectures like CUDA rely on such implementation and add hardware support for optimising coalesced memory accesses, which is in line with the idea of CUDA threads effectively performing vector operations on memory [13] in what we call *wave-fronts* or *warps*.

**The Mali GPUs** do not experience any stalling effect caused by thread divergence. This is because in Mali GPUs, the smallest group of threads with the same program counter is exactly one [14]. As such, any optimisation for preventing thread divergence or for utilising coalesced memory access pattern are unnecessary and may have a negative impact on performance due to strided accesses within kernels.

#### 2.5.3 Vector Operations

Many desktop GPUs operate on scalar types. Mali GPUs, however, have 128-bit registers and support vector operations. Making use of vector operations better utilises the Mali hardware and comes at no cost to the number of concurrent threads <sup>3</sup>. The vector capabilities of the Mali GPU can be seen in Table 2.1.

<sup>&</sup>lt;sup>3</sup>This is of course limited by the amount of registers a kernel requires. If a kernel requires more registers than the device can provide, the amount of concurrently executing work items will be lowered as hardware gets grouped together.

# **Chapter 3**

## **Related Work**

In this chapter we present a series of works related to our research topic. We present the key observations made from these works and present potential issues that were noticed.

Focusing on implementing a neural network execution library means focusing on the underlying mathematical operations such as dense matrix-matrix multiplication, vector operations, convolution, pooling, normalisation, etc... Since there is no such library as the one we are implementing, most of the work is related to these underlying mathematical operations and their performance on the Mali GPUs as well as other low-powered GPUs.

### 3.1 Machine Learning and GPUs

As we approach the physical limits of electronics, we are observing noticeable plateauing of sequential computation performance on CPUs. Parallel platforms like GPUs, however, are consistently increasing in performance and the field of machine learning has been slowly moving towards harnessing the potential of GPUs. Individual studies into this effort for various types of machine learning models have been published, covering many of the essential classification methods such as Naive Bayes [15], K-Means Clustering [16], Decision Trees [17] and Random Forests [18].

In all these works, the performance gains from utilising GPU parallelism have been experimentally demonstrated and their measured results were very significant, motivating further research. However, despite a significant presence of research into machine learning on GPUs, there is a noticeable lack of low-power GPU implementations. In fact, all the research mentioned in this section focused on the CUDA architecture, which is radically different from that on the Mali T-628 GPU (Further discussed in Section 2.5)

### 3.2 Neural Network Frameworks

The idea of having a universal neural network framework is not novel and there are numerous implementations of such frameworks. TensorFlow [19], Caffe [20] or Torch [21] are notable examples, yet there are also frameworks dedicated purely to research in machine learning and deep training, such as Theano [22].

While these frameworks are very popular due to their ease of use and abstraction from the low level nature of GPU device code, they are, much like the research mentioned in Section 3.1, all primarily focused on the CUDA architecture. There is virtually no OpenCL support, despite the overwhelming demand for it from the community [5], and while there may be community-driven incentives for developing OpenCL support independently for some of them (like OpenCL Caffe [23]), these attempts are largely incomplete and (as in the case of OpenCL Caffe), experimental.

### 3.3 Optimising GPU kernels

Memory access patterns are the main deciding factor of how fast a GPU kernel will be, and as such, have been a target of many studies [13] [24] [25]. It is so crucial to optimise memory patterns, that APIs were designed to assist programmers in designing kernels with optimal memory access patterns [26]. Again, however, as noted in Section 3.2, most of this research focuses on CUDA architectures and is not applicable to OpenCL low-powered GPUs like the Mali T-628.

It is worth noting, however, that improvements in kernel performance in these studies have been gained by remapping elements in memory, in order to have a memory access pattern better suited for the particular hardware optimisations. In our work we shall make use of the same general optimisation techniques, yet we shall target them directly at the hardware optimisations of the Mali T-628 GPU.

Research by Anthony E. Nocentino and Philip J. Rhodes [24] into using Z-Morton memory layouts to provide faster access to individual regions of 2-dimensional data has provided the inspiration for using variants of these layouts for optimising matrix multiplication in Chapter 8 of this work.

### 3.4 Optimization Techniques for Mali GPUs

The performance of dense matrix multiplication and two-dimensional convolution (both crucial to neural network evaluation) on a MALI GPU were benchmarked in the 2014 pby Ivan Grasso et. al. [27]. The research entailed implementing a series of conventional algorithms for both the Cortex-A15 (sequential CPU) and the Mali T-604 (parallel GPU) and comparing the relative difference in speed and energy consumption for the implementations. The paper reports a GPU speed-up of up to a factor of 25.5 and 24 for dense matrix multiplication and two-dimensional convolution respectively.

While the results this paper presents are extremely promising for our research, the experimental setup and OpenCL code is not included, meaning the results cannot be reproduced. Furthermore, the performance comparison was done on a Mali T-604 GPU while our research focuses on the later T-628 model. These two models are from the same series and are closely related, so we may expect similar results to be achievable on the Mali T-628 GPU as well.

### 3.5 Mali T-600 Series Matrix Multiplication

Published by ARM, the *Optimising OpenCL kernels for the ARM Mali-T600 GPUs* [12] paper shows the improvements attainable on the single precision general matrixmatrix multiplication algorithm using a variety of kernel optimisations. These include altering memory layouts <sup>1</sup>, vectorization, blocking and cache blocking. The paper demonstrates a 6-fold speed increase between unoptimised and optimised matrixmatrix multiplication kernels and demonstrates the significance of memory barrier overheads.

This paper is one of the few available papers stating Mali board performance metrics in GFLOPS. The research also includes the OpenCL code used to achieve the presented metrics, making the results reproducible (we reproduce the paper's final implementation in Section 7.4). The paper does not, however, specify the workgroup sizes, only presenting the best results seen out of all tried workgroup sizes (we manage to reproduce the best results by inferring optimal workgroup sizes using memory access patterns and workgroup allocation order in Section 7.2).

The single drawback of this paper is that all algorithms and statistics presented in it work with square matrices only, which does not translate well to neural networks, as our matrices may drastically vary in sizes. Once adapted to general matrix sizes, the algorithm presented in Listing 1.12 of the paper proved highly effective for simple memory layouts and is evaluated in Section 7.4 of our research.

### 3.6 CNNdroid

A similar system to that which we are constructing and assessing in this research was released in late 2016 under the name **CNNdroid** [28]. CNNdroid is a neural network execution open source library written in RenderScript [29] and designed for Android phones. It contains implementations for most major neural network operations, such as the dense matrix-matrix multiplication, convolution and max-pooling. As it is written for use on smartphones, this library also includes optimisations for the low-power GPUs (such as vectorisation, see Section 2.5), making it the closest work to this research.

<sup>&</sup>lt;sup>1</sup>This particular paper used transposition to redefine the matrix cross product. This method is, however, exactly equivalent to altering memory layouts.

The primary issue of CNNdroid is that, as it is designed for Android phones and written in RenderScript, it requires Android and the Java virtual machine to run on the device. This may be an undesirable factor when wanting to deploy a neural network execution library to an embedded system with an attached GPU (our system shall be implemented in C++ in order to avoid this kind of overhead).

Furthermore, the optimisation steps taken in CNNdroid do not go beyond the usage of vector types. This is a problem when working with the Mali GPU, since, as we shall demonstrate in this work, techniques such as cache blocking, optimising workgroup sizes, and optimising memory layouts can have a significant positive impact on performance as well, and CNNdroid does not exploit either of these.

# **Chapter 4**

## Infrastructure

This chapter aims at bridging the gap between the low-level of OpenCL with the higher level of C++, and it primarily focuses on the technical side of this project. We present the infrastructure that we built on top of the Khronos C++ OpenCL bindings.

### 4.1 Motivation

During this project we needed to perform an extensive amount of experimentation, benchmarking and statistics gathering for different variations of our kernels. OpenCL compiles device-code for OpenCL devices at runtime and it forces us to manage memory coherency between the host and device in our code. This poses certain complications to our experimentation process, which we shall overcome in this chapter. In order to ensure smooth functioning, our implementation has to ensure the requirements on List 4.1 are met.

The first step we took was to abstract away from the low-level programming of C, for which OpenCL headers are provided. As mentioned in Section 2.3, there exist numerous OpenCL bindings for higher level languages, so for this project, we chose to use the C++ bindings provided by the Khronos Group [10]. This brings the functionality of OpenCL into the context of object oriented programming.

While using  $C^{++}$  bindings for OpenCL brings us into the context of object-oriented programming, we are no closer to satisfying the requirements in List 4.1. Given all these requirements, it became apparent that we require an overarching framework around the  $C^{++}$  bindings, which would satisfy the above requirements.

Such a framework would allow us to focus on the optimisation alone. Writing this framework will hence be the first step we take in this work, and it will subsequently become the foundation for our neural network evaluation system. The framework was named **DynamicCL** and describing its components will be the focus of this chapter.

- 1. Making any changes to the device-code files requires that we re-read and re-compile the up to-date-code.

- 2. Changing the OpenCL device requires all device-code to be recompiled for the new device and all data to be re-synchronised with this new device.

- 3. Any change in the local copy of data requires these changes to be applied to the device memory as well to preserve coherency.

- 4. For every task we need to perform on the device, we may have multiple kernels with different implementations (for benchmarking purposes). Each of these variations may have certain requirements on the input parameters, related to the implementation. Thus changing which implementation we use may require the input argument values to be altered accordingly and synchronised with the device before the kernel is called.

List 4.1: The requirements for the DynamicCL framework

### 4.2 The CLStruct

In order to perform operations on an OpenCL device, we needs a set of objects from the C++ bindings, which wrap the lower level functions of OpenCL. These are the *Platform, Context*, list of *Devices* and a *Command Queue*. Within the DynamicCL framework we keep all this information in one structure called the CLStruct, as shown in Source 4.1.

#### 1 typedef struct {

```

2 std::vector<cl::Platform> platforms;

```

```

3 std::vector<cl::Device> devices;

```

```

4 cl::Context context;

```

```

5 cl::CommandQueue queue;

```

```

6 } CLStruct;

```

#### Source 4.1: The CLStruct

For traversing the list of platforms and devices to find the appropriate device, we have a function called PrepareCL. This function finds the appropriate device and platform, creates an appropriate context and command queue for them and saves them into the CLStruct.

Once the CLStruct is created and filled, it can be used to compile device-code, allocate memory on the device, read and write to device memory, and execute kernels. In other words, it can do everything our requirements state, except, though not on its own. For this purpose we have the **CLManager**, which is described in the next section.

## 4.3 The CLManager

The CLManager class was designed to fulfill requirements 1, 2 and 3 from List 4.1, using an instance of CLStruct. The main public interface methods of this class are in Appendix 12.1.

The methods readLibrary and compileLibrary are related to the first requirement in List 4.1. The CLManager class keeps track of all device-code source files, programs and kernels, ensuring they are always compiled for the appropriate device. Further information on where these kernels are read from is in Section 4.4.1.

The methods createBuffer, deleteBuffer and verify allow us to manage memory, and work similarly to the C functions malloc and free, except they manage GPU memory. They are related to Requirements 3 and 4 from List 4.1. We make further use of these functions in the Mirrorable abstract class, which will be explained in Section 4.5. The CLManager class keeps track of all memory buffers created with the createBuffer method, deleting them when the deleteBuffer method is called. Whether buffers are valid can be checked via the verify method, to ensure no kernels are run on invalid GPU memory buffers.

Finally, we have the setDevice method, which allows us to select an OpenCL device by the number of cores it has. This is related to requirement 2 from List 4.1. For the purposes of our research, this is a sufficient filtration criterion, as both the OpenCL devices visible on the Odroid-XU3 board have different numbers of cores. Once a device is selected, the setDevice method invalidates all programs and buffers (if it had any) and recompiles the source files for the new device via the compileLibrary method.

### 4.4 The DynamicCL::Kernel wrapper

As mentioned in Section 2.3.1, kernels are compiled entry point functions, which can be mapped onto a space of ids. Kernels are wrapped in the cl::Kernel class in the Khronos C++ OpenCL bindings. We, however, wrap the cl::Kernel in a higher class, DynamicCL::Kernel, which provides us with additional simplicity in passing arguments to the kernels. To pass arguments to the kernels, we use the two functions with signatures in Source 4.2. The implementation of these functions takes care of all type conversions, argument counting, and handling of any potential errors.

```

1 // Pass a cl_uint argument to the underlying cl::Kernel

2 Kernel & nextArg(unsigned int longArg);

3

4 // Pass a cl::Buffer to the underlying cl::Kernel

5 Kernel & nextArg(cl::Buffer & buffer);

```

Source 4.2: Primary methods in the DynamicCL::Kernel class

```

{

"sources": [

{

"restrictions": { },

"function": "mat3",

"codename": "mat3",

"source": "lib.cl"

},

{

"codename": "sigmoid1",

"function": "sigmoid1",

"source": "lib.cl",

"restrictions": { },

}

]

}

```

Figure 4.1: Sample content of a Kernel Library JSON file

DynamicCL::Kernel instances can be fetched from the CLManager instance via the getKernel method (see Appendix 12.1). We have, however, not yet explained what the parameter codename is. The codename parameter is a consequence of our kernel organisational structure explained in the next section.

### 4.4.1 Kernel Library JSON File

As stated in the requirements List 4.1, we need to be able to work with more variations of kernels performing the same function. For example, we may have three different variations of a matrix multiplication kernel, each implementation using different optimisations. Thus it is clear that we need to differentiate between *function name* and *functionality*, as many functions can have the same functionality, and for each functionality, we always only use one of them at a time. It is also clear, that if not handled correctly, this could lead to accidental invocation of incorrect kernels, leading to unexpected behaviour.

This is where the Kernel Library JSON File comes into play. When we call the readLibrary method of the CLManager (see Appendix 12.1), we do not pass it a path to the device-code source file. Instead, we pass it the path to the Kernel Library JSON File, which contains a list of all the kernels our program needs. For each kernel, this JSON file contains the name of the device-code function, the name of the file in which the function is located, and a *codename*, with which we can identify the particular kernel in the rest of our codebase. This codename is used to request DynamicCL::Kernel instances from the CLManager via the getKernel method.

A sample set of entries from a Kernel Library JSON File can be seen in Figure 4.1

Note that for every entry in the JSON file in Figure 4.1 there is a key restrictions, which

is, for this example, simply an empty JSON. When a DynamicCL::Kernel instance is requested from the CLManager, the returned instance also contains a reference to this restrictions JSON. The DynamicCL framework does not use this restrictions JSON for anything, it is there for use by the higher level method, which is going to pass arguments to the kernel. This feature will be crucial in Section 8.3.

### 4.5 Mirrorable

This section is aimed at presenting the Mirrorable abstract class. This class bridges the gap between host memory and device memory, by providing us with a simple push/pull interface. The Mirrorable abstract class is designed to wrap itself around a pointer to an array and ensure that a cl:Buffer with device-side memory of adequate size has been allocated for this array on the OpenCL device. The main interface methods provided by the Mirrorable class can be seen in Source 4.3.

```

1 template<typename T>

2 class Mirrorable {

3 public:

4

// Device memory management methods

5

Mirrorable& mirrorTo(const CLManager& manager);

6

int unMirror();

7

bool isMirrored();

8

9

// Synchronisation functions

10

Mirrorable& push();

11

Mirrorable& pull();

12

// Returns the cl::Buffer pointing to the device-side memory

13

14

cl::Buffer & getBuffer();

15

// Virtual size method. used internally by the Mirrorable.

16

17

virtual size_t getSize() = 0;

18

19

// The data itself

20

T * data;

21 \rightarrow

```

Source 4.3: Main interface provided by the Mirrorable abstract class

The Mirrorable class ensures generalisability to other data types via the template T, as well as a great level of automatic failure detection and avoidance. Whenever the mirrorTo method is called, the Mirrorable remembers the reference to the CLManager passed to it as an argument. Thus when the Mirrorable's cl::Buffer is requested via the getBuffer method, the Mirrorable can check that the last cl::Buffer it

fetched is still valid via the CLManager.verify method. If at any point is the buffer *not* valid <sup>1</sup>, the Mirrorable will automatically mirror itself again and push its content to the device, before returning the (now new and valid) cl::Buffer.

The virtual size\_t getSize method is meant to be implementated in child classes. This is due to the fact that the data structure stored in T \* data may be more abstract and its spacial restrictions cannot be generalised. For example, a matrix would have a certain amount of rows and columns, so the getSize method would return a product of these two values. Leaving the getSize method for child class implementation is more general and allows the child class to convey more complex data structures.

### 4.6 Summary

The purpose of this chapter was to give a brief introduction to the DynamicCL framework we wrote. It was written to ensure the automatic management of requirements in List 4.1 and with this framework written we may proceed to build the neural network execution system on top of it.

<sup>&</sup>lt;sup>1</sup>This can happen as a consequence of changing the device in the CLManager instance or calling unMirror on the current Mirrorable

# **Chapter 5**

## **Neural Network Execution System**

In this section we use the DynamicCL framework from Section 4 to construct a system for executing neural networks with OpenCL. Since the goal of this work is to create a system for executing neural networks, not training them, we can limit our implementation to forward propagation only.

As stated in Section 2.1, a neural network is simply a series of affine transformations interleaved with nonlinearities. Therefore, a system capable of forward propagating inputs through a neural network must have all the functionality in List 5.1.

#### 1. Affine Transformation

- Matrix cross product The basis of an affine transformation is a linear transformation using the standard matrix cross product.

- Adding biases An affine transformation involves a translation of data. In neural networks we call this the *bias*.

#### 2. Activation Functions

- Sigmoid function Nonlinearity mapping inputs to the range [0;1]

- **ReLU function** Nonlinearity mapping inputs to the range [0;∞]

List 5.1: List of required functionality of our neural network evaluation framework

### 5.1 The CLMatrix

The first step in implementing the neural network evaluation system is to use the Mirrorable abstract class from Section 4.5 to represent a two-dimensional matrix.

For this purpose we implemented the CLMatrix class. This class stores the size of the matrix in rows and columns. Thanks to the Mirrorable abstract class, the definition for our CLMatrix class is extremely short and can be seen in Source 5.1. This is the basic CLMatrix class and will be further expanded with different optimisations we try in later sections.

```

1 using HonDataType = float;

2 class CLMatrix : public DynamicCL::Mirrorable<HonDataType> {

3 public:

4 size_t cols;

5 size_t rows;

6 size_t getSize() override {

7 return this->rows * this->cols;

8 };

9 }

```

Source 5.1: CLMatrix definition

### 5.1.1 Loading a Matrix into Memory

Since we shall be evaluating pre-trained neural networks, we need a means to load the matrices of these networks into the CLMatrix class. For this we created the Matrix Definition JSON files <sup>1</sup>. These files contain the dimensions of the matrix, the file containing it and information on the file format. An example of such a JSON file can be seen in Figure 5.1.

To load this matrix into the CLMatrix class, we pass the path to the JSON file to a matrix read method. Once the matrix is loaded, we may use the methods provided by the Mirrorable abstract class to mirror the matrix with the GPU and pass it as an argument to kernel functions.

## 5.2 Performers and Operations

In List 4.1 we mentioned that we will have may have multiple kernels with the same functionality, yet different implementations. In this section we introduce a mechanism for switching these implementations in and out of the system, namely the Operations struct and the Performer functions.

<sup>&</sup>lt;sup>1</sup>We parse JSON files using Niels Lohmann's C++ JSON library [30]

```

{

"rows": 50,

"data_type": "csv",

"file": "sample.csv",

"cols": 100

}

```

Figure 5.1: Matrix definition JSON file example. This JSON file defines a 50-by-100 matrix stored in csv format in the file *sample.csv*

The Operations struct will allow us to globally change implementations across the entire system and the performer functions ensure that the kernels are fed correct arguments depending on which functionality we expect they have. Both are further explained in this section.

### 5.2.1 Operations

As mentioned in List 5.1, we need to be able to perform four different operations on the GPU: matrix multiplication, bias addition, sigmoid and ReLU. We may have multiple implementations for each of these, yet we need to be consistent in which one is used at any given moment by the system. We can do this using codenames. Recall from Section 4.3 how individual kernels are requested from the CLManager by their codename. To keep track of which implementations are used at any given time, we implement a struct, which holds the codenames of currently used implementations for each operation (Source 5.2).

```

1 struct Operations {

2   std::string sigmoidCodename = "sigmoid1";

3   std::string reluCodename = "relu1";

4   std::string matmulCodeName = "cross1";

5   std::string biasAddCodename = "colAddRM";

6 };

```

Source 5.2: Operations struct. Used to hold the codenames of current implementations of each functionality.

It is crucial that there is only one instance of this Operations struct (or that multiple instances are handled with caution). Any classes and structures we create in subsequent sections of this chapter will hold C++ references to the std::string fields in this struct (or references to the struct itself). This allows us to globally change the implementation of any operation by simply changing the corresponding field in the Operations struct.

### 5.2.2 Performer Methods

Performers are the final step of abstraction from the low levels of OpenCL. They wrap within themselves the calls to our CLManager and the passing of arguments to our DynamicCL::Kernel instances. They allow us to perform high-level operations (like matrix multiplication) on high-level classes (the CLMatrix).

The idea is simple: no matter how many implementations of each operation we have, they are still going to have similar (or in many cases identical) method signatures. Thus for each operation we define a static method, which contains the process of passing arguments to the kernels and launching kernels corresponding to the particular operation. This static method then gets called from other places in the code whenever the operation is required (may be called from within Layer objects in the neural network).

A further task the performer methods do is related to the *restrictions* key in every kernel definition of the Kernel Definition JSON File from Section 4.4.1. We will further explain how these restrictions are useful in Section 8.3, as we have not yet introduced the particular situations in which their purpose is utilised.

## 5.3 The Neural Network

In this section we present the way in which we represent neural networks in terms of CLMatrix objects. The networks contain two kinds of layers, namely Affine Layers and Activation Layers, and out of a Model object, which chains these layers together. We also present a mechanism for loading neural networks from files using the Neural Network Definition JSON File.

We shall have three layer types: AffineLayer, SigmoidLayer and ReLULayer. For each layer type we implement an object, which extends the base Layer class seen in Source 5.2. As such, every layer will have an fprop method, which can be used to forward propagate values over the network.

```

1

class Layer {

2

public:

3

virtual CLMatrix& fprop(

4

DynamicCL::CLManager& manager,

5

CLMatrix& inputs, int& time

6

) = 0;

7

virtual void display() = 0;

8

};

```

Figure 5.2: Interface of every Layer object.

### 5.3.1 Neural Network Definition JSON File

In Section 5.1.1 we presented a way of loading matrices into CLMatrix objects. In this section we present a similar way of defining neural networks in JSON files. A sample file can be seen in Figure 5.3. The Neural Network Definition JSON File contains a list of JSONs, each of which contains a *layer* key describing the layer type, as well as additional keys, specific to the particular layer type.

Being activation functions, neither the sigmoid Layer nor the ReLU layer require any parameters for functioning. The affine layer needs to know what weights and biases it is to be using. Hence the affine layer definitions contain the keys *weights* and *biases*, which contain the relative path to their respective Matrix Definition JSON files we mentioned in Section 5.1.1.

With this configuration, our program may now load arbitrary fully-connected feedforward neural networks into Model objects and forward propagate values over it by passing the input values to its Model.fprop method.

```

{

"layers": [

{

"layer": "AffineLayer",

"weights": "1_w.json",

"biases": "1 b.json"

},

{

"layer": "SigmoidLayer"

},

{

"layer": "AffineLayer",

"weights": "2_w.json",

"biases": "2_b.json"

},

{

"layer": "SigmoidLayer"

},

{

"layer": "AffineLayer",

"weights": "3_w.json",

"biases": "3_b.json"

}

],

"size": 5

}

```

Figure 5.3: Sample neural network definition JSON file

#### 5.3.2 Affine Layer Execution

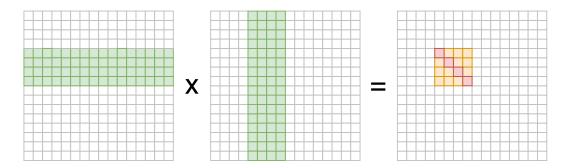

Due to the non-commutativity of matrix multiplication, it is important to clarify how exactly the affine layer forward propagates values. Suppose we have *n* input vectors  $\bar{v}$  of dimensionality *d* and we want to feed them into an affine layer, which transforms them into *h* dimensional vectors. The input to an affine layer is will be a matrix *I* with *d* rows and *n* columns. The weight matrix *W* has *h* rows and *d* columns, and the bias matrix *b* has *h* rows and one column.

The input matrix is:

$$I = \left[\bar{v}_1, \bar{v}_2, \bar{v}_3 \cdots \bar{v}_n\right]$$

The resulting matrix *R* is computed by the affine layer as:

$$R = W \times I + b$$

This should clear any ambiguity in the implementation of kernels in future sections.

### 5.4 Summary

The goal of this chapter was to introduce our neural network execution system. The system enables loading neural network models from files, mirroring them to GPU memory and executing the appropriate OpenCL kernels for individual mathematical operations needed to forward propagate inputs over the loaded network. With this system completed, we may now address the writing and optimisation of the individual kernels to maximise forward propagation performance on the Mali T-628 GPU.

## **Chapter 6**

## **Baseline**

As a baseline, we are going to implement very elementary, unoptimised versions for the matrix multiplication, bias addition and the sigmoid activation function. We shall then use this setup to forward propagate values through a sample neural network and attempt to use the measured results to identify bottlenecks.

### 6.1 Matrix Multiplication

We shall begin with the matrix multiplication. As we know, the product of two matrices *A* and *B* of dimensions  $a \times b$  and  $b \times c$  respectively is a matrix *C* of dimensions  $a \times c$  with each element  $C_{ij}$  calculated as:

$$C_{ij} = \sum_{k=1}^{b} \left( A_{ik} \times B_{kj} \right)$$

The stronger of the two Mali T-628 GPU OpenCL devices has 4 compute units, each of which can run 256 work items at the same time (as seen in Table 2.1). In our baseline we are going to have one work item compute one element of the resulting matrix. We are thus going to be mapping our kernel to a two-dimensional space of ids equivalent to:

$$\{0...(a-1)\} \times \{0...(c-1)\}$$

We shall not be specifying the workgroup size, as this is the focus of investigation in future sections. OpenCL has an automatic system for grouping the work items into workgroups, albeit it is not always the most effective. For our baseline, however, it will be sufficient. The kernel we implemented can be found in Source 6.1.

```

1

_kernel void cross1( uint 1, uint w,

2

global const HON_DATA_TYPE* a,

3

global const HON_DATA_TYPE * b,

4

global HON_DATA_TYPE * c)

5

{

6

7

size_t row = get_global_id(0);

8

size t col = get global id(1);

9

HON_DATA_TYPE cumulative = 0;

10

for (int i = 0; i < 1; i++) {</pre>

11

cumulative += a[row*l + i] * b[w*i + col];

12

}

13

c[row*w + col] = cumulative;

14 }

```

Source 6.1: Matrix multiplication baseline kernel. Parameter 1 stands for the length of the conjoining dimension of the matrices, while w stands for the width of the matrix

### 6.2 Sigmoid Function

The sigmoid activation function transforms the elements of the matrix with the logistic sigmoid function. The dimensions of the matrix remain the same. All elements of the matrix are computed as:

$$B_{ij} = \frac{1}{1 + e^{-A_{ij}}}$$

We shall once again compute each element in the resulting matrix in a single work item, much like we have done in the previous section for matrix multiplication. In contrast to the previous section, however, we are going to perform the transformation in place, that is, we shall replace the initial values with the transformed ones without moving them to a new matrix elsewhere in memory.

The kernel for this transformation can be seen in Source 6.2.

```

1 kernel void sigmoid1(global HON_DATA_TYPE * mat) {

2 size_t index = get_global_id(0);

3 mat[index] = 1.0 / (1 + exp(-mat[index]));

4 }

```

Source 6.2: Sigmoid activation baseline kernel

## 6.3 Bias Addition

Bias addition is the process of translating the individual features of each input vector by a certain quantity. In our research, inputs are represented as columns in forward propagating matrices. As such, the biases must also be a column matrix of size  $d \times 1$ , where *d* is the dimensionality of the input feature vectors.

Translating a matrix A by a bias vector b into the resulting matrix C is computed as follows:

$$C_{ij} = A_{ij} + b_i$$

We shall once again compute each element in the resulting matrix in a separate work item, mapping the bias addition kernel to the same two dimensional range as in Section 6.1. We are also going to perform this operation in place, storing the result in the corresponding location in the origin matrix.

The baseline bias addition kernel can be seen in Source 6.3

```

__kernel void colAddRM(uint rows, uint cols,

1

2

global HON_DATA_TYPE * mat,

3

global HON_DATA_TYPE * column)

4

{

5

size_t row = get_global_id(0);

size_t col = get_global_id(1);

6

7

mat[col + row*cols] += column[row];

8

}

```

Source 6.3: Bias addition baseline kernel

## 6.4 Evaluation

In order to evaluate the performance of our baseline system, we decided to train a small neural network on classifying the MNIST [31] picture set and use our system to classify 1000 of these images. The MNIST picture set is a dataset of 28-by-28 pixel hand written digits, equating to 784 features per input vector.

We trained a three layer neural network with three layers of widths 100, 100 and 10 neurons respectively, each but the last followed by a sigmoid layer. The neural network definition JSON file for this network is the one in Figure 5.3.

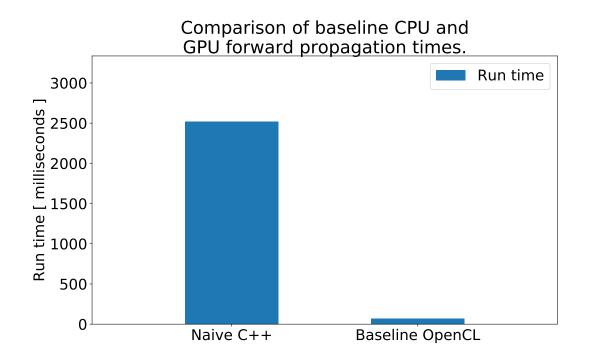

Figure 6.1: Time taken to forward propagate our baseline model. Run times are compared between time taken on a CPU (left) and time taken on a GPU with our implementation (right).

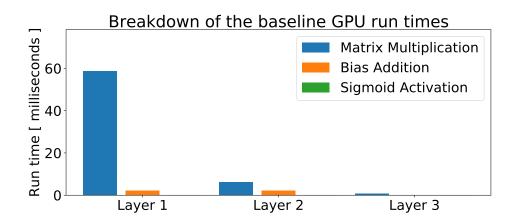

Figure 6.2: The breakdown of operation kernel run time for every operation in the baseline neural network. Plotted values are the average of ten measurements with negligible standard error (invisible on graph). The run time of activation layers was also negligibly small and invisible.

## 6.5 Summary

It is clear from Figure 6.1 that there is a significant gain in classification speed when using the Mali-T628 GPU on the Odroid board as opposed to simply using a sequential CPU implementation.

We can now further investigate the performance of our OpenCL baseline by breaking the runtime down into the individual kernels in order to find the main bottleneck. You can see this breakdown in Figure 6.2.

It is quite clear that the matrix multiplication is the primary bottleneck of our system. This was expected, as matrix multiplication is the most complex operation we use. The algorithm we use to compute the product of two matrices A and B with dimensions  $a \times b$  and  $b \times c$  respectively has complexity of O(abc). It is also clear that matrix multiplication should be expected to take more time, as it is the only operation the kernel of which has a loop inside it, yet for every operation we run the same amount of work items.

# **Chapter 7**

## **Optimizing the Matrix Multiplication**

In our baseline we have observed that matrix multiplication is the major bottleneck of our current implementation. In this chapter we optimise matrix multiplication using a variety of techniques including altering memory layouts, optimising workgroup sizes, vectorising the operation and blocking.

Our baseline implementation for this operation is the standard matrix multiplication algorithm which, for square matrices of dimensions  $n \times n$ , has a complexity of  $O(n^3)$ . It is worth mentioning that there exist better methods with lower complexities, such as Strassen's algorithm, with complexity of  $O(n^{\log_7(8)})$  [32]. However, the benefits of using these algorithms becomes more apparent only once the sizes of the matrices reach the fifth order of magnitude, where a perfromance increase of roughly 32% may be achieved [32]. In this report we focus primarily on optimising by better utilizing available hardware rather than changing algorithms, as this yields considerably higher performance gains (up to 4000% in the final optimization stage).

## 7.1 Memory Layouts

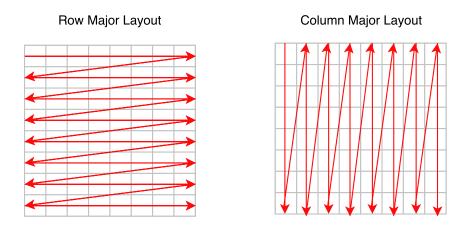

The way a matrix is represented and stored in memory can significantly impact performance. Matrices are, conceptually, two-dimensional tables of numbers, however, computer memory is strictly one-dimensional. There are two main layouts in which a matrix can be represented in memory: **row major layout** (RM) and **column major layout** (CM). A graphical representation how the data is stored in memory with these layouts can be seen in Figure 7.1.

row major and column major layouts and their effect on matrix multiplication were explored by Johan Gronqvist and Anton Lokhmotov[12]. In this paper they referred to the layouts as **transposed** and **non-transposed**, and proceeded to redefine the cross product operation to compensate these transformations. We are, however, going to think of them in terms of row major and column major, as they have identical effects and open doors to explore various more complex layouts (Chapter 8).

For this work, we shall use the memory access notation presented in Johan Gronqvist's

Figure 7.1: Row major and column major memory layouts

and Anton Lokhmotov's paper [12], with the slight alteration of replacing the comma with an up arrow indicating the direction of the accesses (more on this notation can be found in Appendix 12.8). In this notation, we may express the memory access pattern of our baseline matrix multiplication algorithm as seen in Equation 7.1. Equation 7.1 shows how the baseline matrix multiplication kernel accesses matrix *B* with a stride of size *c*.

$$\stackrel{b}{\uparrow}_{k=0} \left( A[ib+k], B[kc+j] \right)$$

Equation 7.1: Memory access pattern of a work item *i*, *j* in the baseline matrix multiplication kernel from Section 6.1, when multiplying matrices  $A \times B$  of dimensions  $a \times b$  and  $b \times c$  respectively.

Accessing memory on the Mali GPU in strides is undesirable. We have established in Section 2.5.2 that Mali GPUs do not have hardware optimisation designated to coalesced memory accesses and all memory access optimisation is heavily cache-based. Strided memory accesses imply cache misses with *every* iteration of the loop. This means we may expect kernels which access memory sequentially, to perform better than strided kernels <sup>1</sup> and as such, that our current memory layout is sub-optimal.

In this section, we propose keeping the right-hand side matrix of the matrix multiplication kernel in Column Major form as a means of mitigating the rate of cache misses.

With this new proposed memory layout, every work item will be accessing data sequentially from both matrices while iterating through the for loop of the kernel. This way a cache miss will occur for both lines every 16 iterations, when the loop reaches the end of a cache line (one cache line fits 16 float values). This is significantly better than our baseline kernel, where cache misses occurred with *every* iteration.

This new proposed kernel has a memory access pattern as described in Equation 7.2

<sup>&</sup>lt;sup>1</sup>strided kernels perform well on CUDA architecture, when concurrent work items of identical strides access coalesced memory simultaneously with every iteration of a loop

#### 7.1. Memory Layouts

$$\stackrel{b}{\uparrow}_{k=0} \left( A[ib+k], B[jb+k] \right)$$

Equation 7.2: Memory access pattern of a work item i, j in the Row Major × Column Major (RM×CM) matrix multiplication kernel when multiplying matrices  $A \times B$  of dimensions  $a \times b$  and  $b \times c$  respectively.

(all access patterns are sequential). The kernel implementation can be found in Source 7.1.

```

1

__kernel void cross1( uint 1, uint h,

2

global const HON_DATA_TYPE * a,

3

global const HON_DATA_TYPE * b,

4

global HON_DATA_TYPE * c)

5

{

6

7

size_t row = get_global_id(0);

8

size_t col = get_global_id(1);

9

HON_DATA_TYPE cumulative = 0;

10

11

for (int i = 0; i < 1; i++) {

12

cumulative += a[row*l + i] * b[col*l + i];

13

}

14

c[col*h + row] = cumulative;

15 }

```

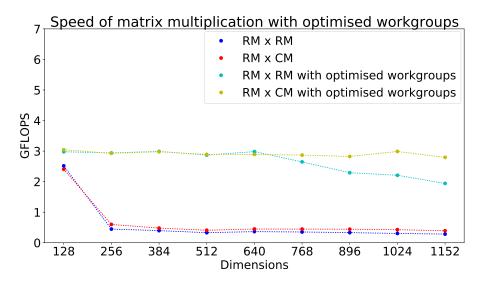

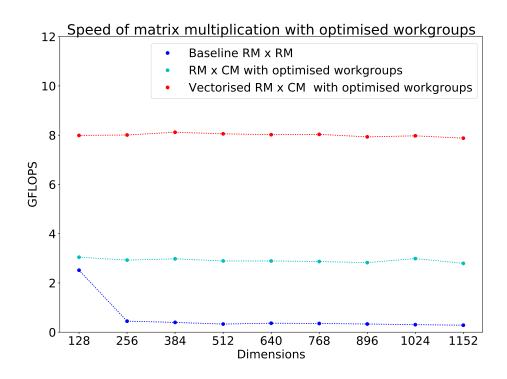

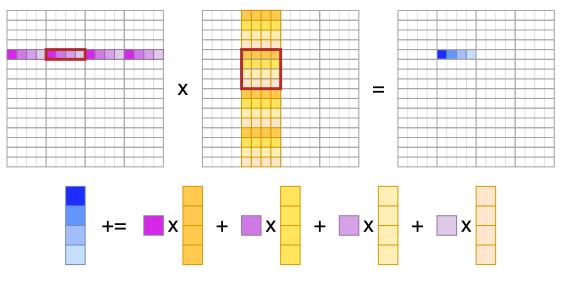

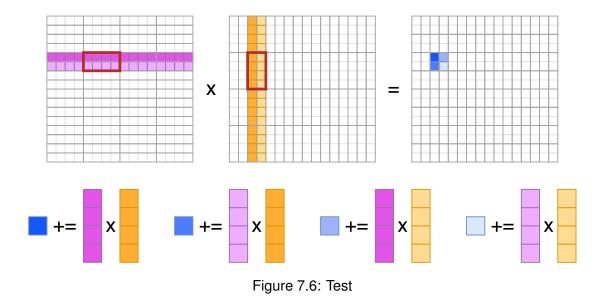

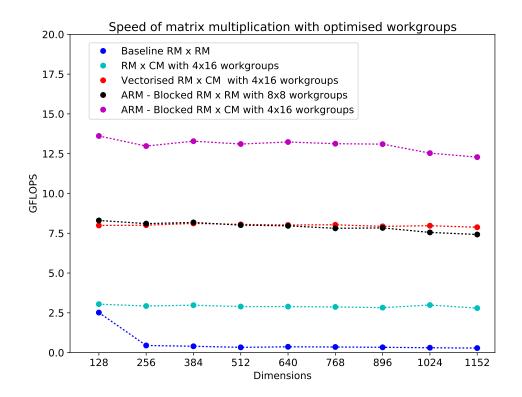

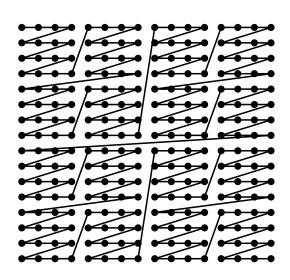

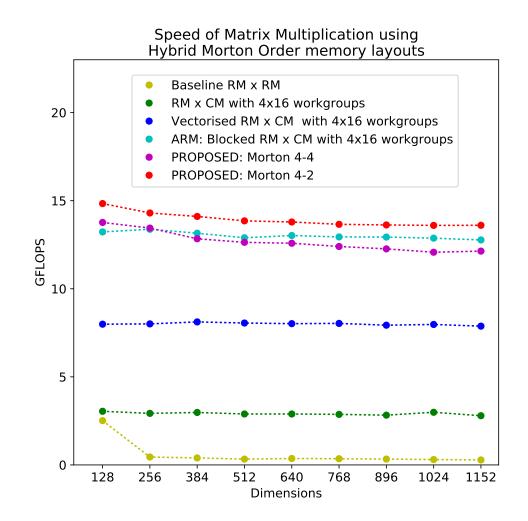

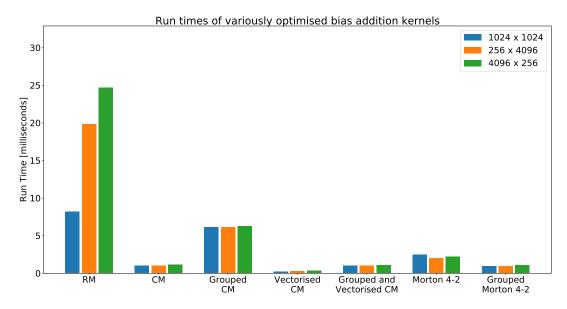

Source 7.1: Matrix multiplication kernel with optimised memory layouts. Parameter 1 stands for the length of the conjoining dimension of the matrices, while h stands for the height of the resulting matrix. Expects matrix a to be in row major layout and b to be in column major layout. Resulting matrix is saved in column major layout.